## ספריות הטכניון The Technion Libraries

בית הספר ללימודי מוסמכים ע"ש ארווין וג'ואן ג'ייקובס Irwin and Joan Jacobs Graduate School

## All rights reserved to the author

This work, in whole or in part, may not be copied (in any media), printed, translated, stored in a retrieval system, transmitted via the internet or other electronic means, except for "fair use" of brief quotations for academic instruction, criticism, or research purposes only.

Commercial use of this material is completely prohibited.

#### © כל הזכויות שמורות למחבר/ת

אין להעתיק (במדיה כלשהי), להדפיס, לתרגם, לאחסן במאגר מידע, להפיץ באינטרנט, חיבור זה או כל חלק ממנו, למעט "שימוש הוגן" בקטעים קצרים מן החיבור למטרות לימוד, הוראה, ביקורת או מחקר. שימוש מסחרי בחומר הכלול בחיבור זה אסור בהחלט.

# Concurrent Data Structures for Non-Volatile Memory

Michal-Evgenia Korenberg (Friedman)

## Concurrent Data Structures for Non-Volatile Memory

Research Thesis

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Michal-Evgenia Korenberg (Friedman)

Submitted to the Senate of the Technion — Israel Institute of Technology Tishri 5782 — Haifa — September 2021 This research was carried out under the supervision of Prof. Erez Petrank, in the Faculty of Computer Science.

Some results in this thesis have been published as articles by the author and research collaborators in conferences and journals during the course of the author's doctoral research period, the most up-to-date versions of which being:

Michal Friedman, Maurice Herlihy, Virendra Marathe, and Erez Petrank. A persistent lock-free queue for non-volatile memory. In *ACM Symposium on Principles and Practice of Parallel Programming (PPOPP)*, volume 53, pages 28–40. ACM, 2018.

Naama Ben-David, Guy Blelloch, Michal Friedman, and Yuanhao Wei. Delay-free concurrency on faulty persistent memory,. In *ACM Symposium on Parallelism in Algorithms and Architectures (SPAA)*, 2019.

Michal Friedman, Naama Ben-David, Yuanhao Wei, Guy Blelloch, and Erez Petrank. Nvtraverse: In nvram data structures, the destination is more important than the journey. In ACM Conference on Programming Language Design and Implementation (PLDI).

Michal Friedman, Erez Petrank, and Pedro Ramalhete. Mirror: Making lock-free data structures persistent. In ACM Conference on Programming Language Design and Implementation (PLDI), pages 1218—1232, 2021.

Yuanhao Wei, Naama Ben-David, Michal Friedman, Guy Blelloch, and Erez Petrank. Flit: A library for simple and efficient persistent algorithms, 2021.

#### Acknowledgements

I would like to express my deepest appreciation and gratitude to my amazing advisor, Erez Petrank, for his guidance and support. I've had a huge privilege of working with an incredible researcher and adviser who taught me a huge set of professional and personal skills during my PhD. I would like to thank Erez for his constant belief in me and for being much more than an advisor to me.

I had the pleasure to work with my co-authors from which I have learned a great deal, had a lot of fun, and inspired me a lot: Naama Ben-David, Guy Blelloch, Nachshon Cohen, Maurice Herlihy, Jim Larus, Virendra Marathe, Erez Petrank, Pedro Ramalhete, Gali Sheffi, Yuanhao Wei, and Yoav Zuriel.

I thank my candidacy exam committee, Yehuda Afek, Roy Friedman, Yoram Moses, and Assaf Schuster for their time, wisdom, and advice. I also thank my final exam committee, Yehuda Afek and Roy Friedman, for their insightful comments.

I would also like to thank David Bacon who hosted me for an internship at Google New York in the summer of 2017. This internship, although not directly related to the main line of my thesis, had contributed a lot to my skill set.

The Computer Science Department was my second home and I am thankful to its administrative and academic staff for that. I thank my incredible friends that I've met along the way. I am blessed to have you in my life.

I am thankful to my family and in particular my mother for her encouragement to excel and her endless belief in me. And a last and unique thank you to my one and only, my life partner, my husband Amit. I could not have done this without you. You provide me with motivation, advice, endless love and support, which helps put everything into perspective. I dedicate this work to you.

The Technion's and Azrieli's Foundation funding of this research is hereby acknowledged.

## Contents

#### List of Figures

| A        | Abstract 1 |              |                                       |    |  |

|----------|------------|--------------|---------------------------------------|----|--|

| 1        | Intr       | Introduction |                                       |    |  |

|          | 1.1        | Persis       | tent Transactions                     | 4  |  |

|          | 1.2        | Hand-        | Tuned Constructions                   | 4  |  |

|          | 1.3        | Gener        | al Constructions                      | 5  |  |

|          | 1.4        | Correc       | ctness Conditions and Detectability   | 7  |  |

|          | 1.5        | Contr        | ibutions                              | 8  |  |

|          | 1.6        | Perspe       | ective                                | 8  |  |

|          | 1.7        | Thesis       | s Structure                           | 9  |  |

| <b>2</b> | Pre        | limina       | ries                                  | 11 |  |

| _        | 2.1        | Model        |                                       | 11 |  |

|          | 2.2        |              | ctness and Progress Conditions        | 13 |  |

|          |            |              |                                       |    |  |

| 3        | A H        | Iand-T       | Cuned Construction: A Lock-Free Queue | 17 |  |

|          | 3.1        | Introd       | luction                               | 17 |  |

|          | 3.2        | Prelin       | ninaries                              | 18 |  |

|          |            | 3.2.1        | The MS Queue                          | 18 |  |

|          |            | 3.2.2        | Hardware Instructions for Persistence | 19 |  |

|          | 3.3        | An O         | verview of the Three Queue Designs    | 19 |  |

|          |            | 3.3.1        | The Durable Queue                     | 20 |  |

|          |            | 3.3.2        | The Log Queue                         | 21 |  |

|          |            | 3.3.3        | The Relaxed Queue                     | 23 |  |

|          | 3.4        | Algori       | thm Details of the Durable Queue      | 24 |  |

|          |            | 3.4.1        | The Enqueue() Operation               | 26 |  |

|          |            | 3.4.2        | The Dequeue() Operation               | 27 |  |

|          |            | 3.4.3        | The Recovery() Operation              | 27 |  |

|          |            | 3.4.4        | Correctness                           | 29 |  |

|          | 3.5        | Algori       | thm Details of the Log Queue          | 29 |  |

|          |            | 3.5.1        | The Enqueue() Operation               | 32 |  |

|   |      | 3.5.2                      | The Dequeue() Operation               | 2 |

|---|------|----------------------------|---------------------------------------|---|

|   |      | 3.5.3                      | The Recovery() Operation              | 4 |

|   | 3.6  | Algorit                    | thm Details of the Relaxed Queue      | 5 |

|   |      | 3.6.1                      | The Enqueue() Operation               | 7 |

|   |      | 3.6.2                      | The Dequeue() Operation               | 8 |

|   |      | 3.6.3                      | The Sync() Operation                  | 8 |

|   |      | 3.6.4                      | The Recovery() Operation              | 0 |

|   | 3.7  | Memor                      | ry Management                         | 0 |

|   | 3.8  | Measur                     | rements                               | 1 |

|   |      | 3.8.1                      | Optimizations                         | 4 |

|   | 3.9  | Related                    | d Work                                | 4 |

|   | 3.10 | Conclu                     | sion                                  | 5 |

| 4 | A G  | Construction: NVTraverse 4 | 9                                     |   |

|   | 4.1  | Introdu                    | action                                | 9 |

|   | 4.2  | Prelim                     | inaries                               | 1 |

|   |      | 4.2.1                      | Running Example: Harris's Linked List | 1 |

|   | 4.3  | Travers                    | sal Data Structures                   | 2 |

|   |      | 4.3.1                      | Traversal                             | 4 |

|   |      | 4.3.2                      | Critical Method: Node Disconnection   | 6 |

|   |      | 4.3.3                      | Algorithmic Supplements               | 8 |

|   | 4.4  | NVTra                      | verse Data Structures                 | 9 |

|   |      | 4.4.1                      | Recovery                              | 9 |

|   |      | 4.4.2                      | Before the Critical Method            | 0 |

|   |      | 4.4.3                      | During the Critical Method 6          | 3 |

|   | 4.5  | Correct                    | tness                                 | 4 |

|   | 4.6  | Examp                      | de                                    | 2 |

|   | 4.7  | Experi                     | mental Evaluation                     | 3 |

|   |      | 4.7.1                      | Setup                                 | 7 |

|   |      | 4.7.2                      | Results on NVRAM                      | 7 |

|   |      | 4.7.3                      | Results on DRAM                       | 0 |

|   |      | 4.7.4                      | Other Architectures                   | 3 |

|   | 4.8  | Related                    | d Work                                | 3 |

|   | 4.9  | Conclu                     | sions                                 | 4 |

| 5 | A G  | eneral                     | Construction: Mirror 8                | 5 |

|   | 5.1  | Introduction               |                                       | 5 |

|   | 5.2  | The M                      | irror Library                         | 6 |

|   |      | 5.2.1                      | Replica Location                      | 7 |

|   |      | 5.2.2                      | Interface                             | 7 |

|   | 5.3  | Mirror                     | Underlying Mechanism                  | 8 |

|                        | 5.3.1                                                                                                              | Implementation                                                                                                                                                                                                                                                                 | . 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | 5.3.2                                                                                                              | Persistent Roots                                                                                                                                                                                                                                                               | . 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 5.3.3                                                                                                              | Memory Reclamation                                                                                                                                                                                                                                                             | . 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.4                    | Correc                                                                                                             | ctness                                                                                                                                                                                                                                                                         | . 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.5                    | Evalua                                                                                                             | ation                                                                                                                                                                                                                                                                          | . 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 5.5.1                                                                                                              | Experimental Setup                                                                                                                                                                                                                                                             | . 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 5.5.2                                                                                                              | One Replica on DRAM                                                                                                                                                                                                                                                            | . 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 5.5.3                                                                                                              | Mirror with Both Replicas on NVMM                                                                                                                                                                                                                                              | . 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.6                    | Relate                                                                                                             | ed Work                                                                                                                                                                                                                                                                        | . 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.7                    | Concl                                                                                                              | usions                                                                                                                                                                                                                                                                         | . 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A L                    | ibrary                                                                                                             | for Efficient Persistence: Flit                                                                                                                                                                                                                                                | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1                    | Introd                                                                                                             | luction                                                                                                                                                                                                                                                                        | . 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.2                    | Prelin                                                                                                             | ninaries                                                                                                                                                                                                                                                                       | . 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.3                    | Persis                                                                                                             | tent-Volatile Instruction Interface                                                                                                                                                                                                                                            | . 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 6.3.1                                                                                                              | Applicability of the P-V Interface                                                                                                                                                                                                                                             | . 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.4                    | The F                                                                                                              | liT Library and Interface                                                                                                                                                                                                                                                      | . 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.5                    | The A                                                                                                              | Algorithm                                                                                                                                                                                                                                                                      | . 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 6.5.1                                                                                                              | Placement of the Counter                                                                                                                                                                                                                                                       | . 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.6                    | Evalua                                                                                                             | ation                                                                                                                                                                                                                                                                          | . 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 6.6.1                                                                                                              | Setup                                                                                                                                                                                                                                                                          | . 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

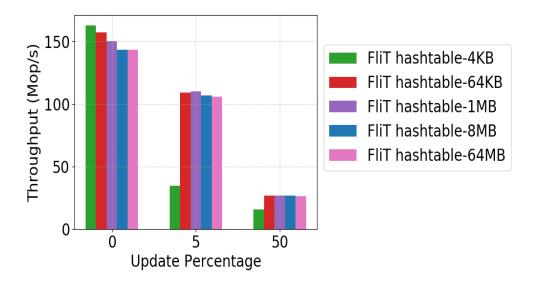

|                        | 6.6.2                                                                                                              | FliT Hash Table Size                                                                                                                                                                                                                                                           | . 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

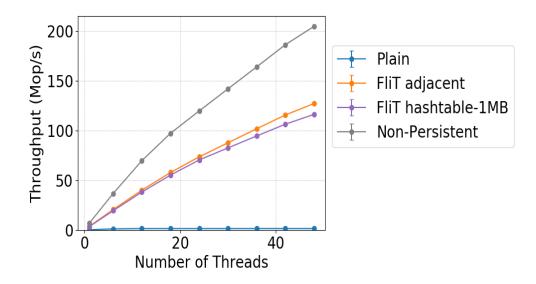

|                        | 6.6.3                                                                                                              | Varying Number of Threads                                                                                                                                                                                                                                                      | . 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

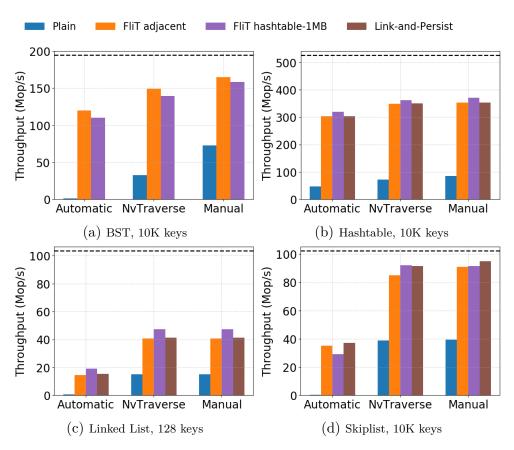

|                        | 6.6.4                                                                                                              | Comparing Durability Methods                                                                                                                                                                                                                                                   | . 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

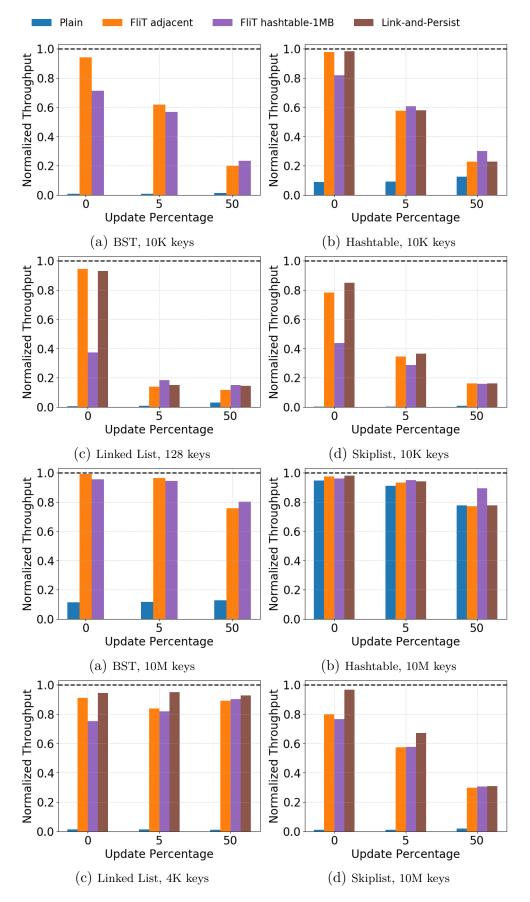

|                        | 6.6.5                                                                                                              | Effect of updates                                                                                                                                                                                                                                                              | . 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 6.6.6                                                                                                              | Comparing FliT and Link-and-Persist                                                                                                                                                                                                                                            | . 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 6.6.7                                                                                                              | Effect of Data Structure Size on Performance                                                                                                                                                                                                                                   | . 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

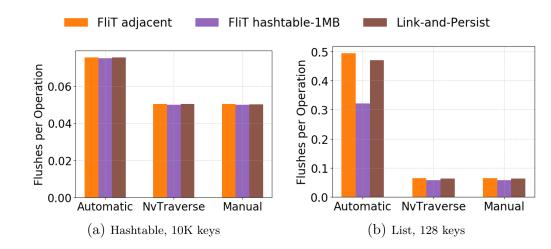

|                        | 6.6.8                                                                                                              | Measuring Number of Flushes                                                                                                                                                                                                                                                    | . 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.7                    | Relate                                                                                                             | ed Work                                                                                                                                                                                                                                                                        | . 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.8                    | Concl                                                                                                              | usion                                                                                                                                                                                                                                                                          | . 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $\mathbf{W}\mathbf{h}$ | ole Pr                                                                                                             | ogram Persistence                                                                                                                                                                                                                                                              | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7.1                    | Introd                                                                                                             | luction                                                                                                                                                                                                                                                                        | . 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.2                    | Prelin                                                                                                             | ninaries                                                                                                                                                                                                                                                                       | . 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 7.2.1                                                                                                              | Capsules                                                                                                                                                                                                                                                                       | . 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.3                    | k-Dela                                                                                                             | ay Simulations                                                                                                                                                                                                                                                                 | . 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.4                    | Buildi                                                                                                             | ing Blocks                                                                                                                                                                                                                                                                     | . 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 7.4.1                                                                                                              | Capsule Implementation                                                                                                                                                                                                                                                         | . 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 7.4.2                                                                                                              | Recoverable Primitives                                                                                                                                                                                                                                                         | . 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.5                    | Persis                                                                                                             | ting Concurrent Programs                                                                                                                                                                                                                                                       | . 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7.6                    |                                                                                                                    |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        | 5.5<br>5.6<br>5.7<br><b>A</b> L<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Wh</b><br>7.1<br>7.2<br>7.3<br>7.4 | 5.3.3 5.4 Correct 5.5 Evalue 5.5.1 5.5.2 5.5.3 5.6 Relate 5.7 Concle  A Library 6.1 Introd 6.2 Prelin 6.3 Persis 6.3.1 6.4 The Fence Fence 6.5.1 6.6 Evalue 6.6.1 6.6.2 6.6.3 6.6.4 6.6.5 6.6.6 6.6.7 6.6.8 6.7 6.6.8 6.7 7.2 Prelin 7.2.1 7.3 k-Delate 7.4.1 7.4.2 7.5 Persis | 5.3.2 Persistent Roots 5.3.3 Memory Reclamation  5.4 Correctness  5.5 Evaluation 5.5.1 Experimental Setup 5.5.2 One Replica on DRAM 5.5.3 Mirror with Both Replicas on NVMM  5.6 Related Work 5.7 Conclusions  A Library for Efficient Persistence: Flit 6.1 Introduction 6.2 Preliminaries 6.3 Persistent-Volatile Instruction Interface 6.3.1 Applicability of the P-V Interface 6.4 The FliT Library and Interface 6.5 The Algorithm 6.5.1 Placement of the Counter  6.6 Evaluation 6.6.1 Setup 6.6.2 FliT Hash Table Size 6.6.3 Varying Number of Threads 6.6.4 Comparing Durability Methods 6.6.5 Effect of updates 6.6.6 Comparing FliT and Link-and-Persist 6.6.7 Related Work 6.8 Conclusion  Whole Program Persistence 7.1 Introduction 7.2 Preliminaries 7.2.1 Capsules 7.3 k-Delay Simulations 7.4 Building Blocks 7.4.1 Capsule Implementation 7.4.2 Recoverable Primitives 7.5 Persisting Concurrent Programs |

| Н | Hebrew Abstract |         |                            |       |

|---|-----------------|---------|----------------------------|-------|

| 8 | Cor             | nclusio | n                          | 161   |

|   | 7.8             | Exper   | iments                     | . 157 |

|   | 7.7             | Practi  | ical Concerns              | . 153 |

|   |                 | 7.6.3   | Handling Write-CAS races   | . 152 |

|   |                 | 7.6.2   | Normalized Data Structures | . 148 |

|   |                 | 7.6.1   | CAS-Read Capsules          | . 146 |

## List of Figures

| 3.1  | Internal Durable Queue classes                                         | 25 |

|------|------------------------------------------------------------------------|----|

| 3.2  | The enqueue operation of Durable Queue                                 | 26 |

| 3.3  | The dequeue operation of Durable Queue                                 | 28 |

| 3.4  | Internal Log Queue classes                                             | 30 |

| 3.5  | The enqueue operation of Log Queue                                     | 31 |

| 3.6  | The dequeue operation of Log Queue                                     | 33 |

| 3.7  | Internal Relaxed Queue classes                                         | 36 |

| 3.8  | The enqueue method of the Relaxed Queue                                | 37 |

| 3.9  | The dequeue method of the Relaxed Queue                                | 38 |

| 3.10 | The sync method of the Relaxed Queue                                   | 39 |

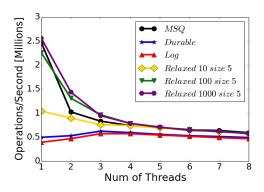

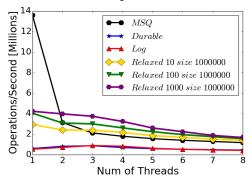

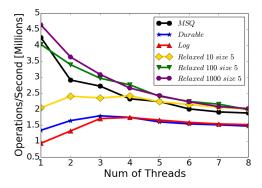

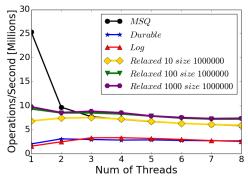

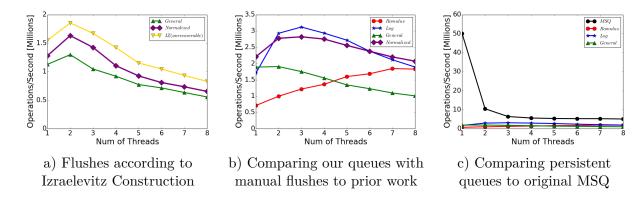

| 3.11 | Throughput of the various queue implementations with memory man-       |    |

|      | agement on the $\mathbf{AMD}$ platform                                 | 46 |

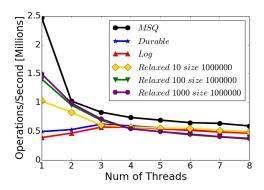

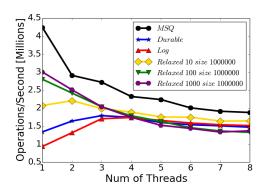

| 3.12 | Throughput of the various queue implementations with memory man-       |    |

|      | agement on the $\mathbf{AMD}$ platform                                 | 46 |

| 3.13 | Throughput of the various queue implementations with no object reuse   |    |

|      | on the AMD platform                                                    | 46 |

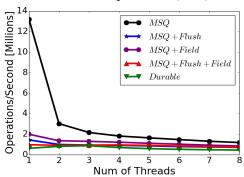

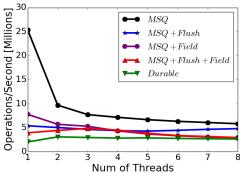

| 3.14 | MSQ, only flushes added, flushes and additional fields, and the entire |    |

|      | durable queue on the $\mathbf{AMD}$ platform                           | 46 |

| 3.15 | Throughput of the various queue implementations with memory man-       |    |

|      | agement on the Intel platform                                          | 47 |

| 3.16 | Throughput of the various queue implementations with memory man-       |    |

|      | agement on the Intel platform                                          | 47 |

| 3.17 | Throughput of the various queue implementations with no object reuse   |    |

|      | on the Intel platform                                                  | 47 |

| 3.18 | MSQ, only flushes added, flushes and additional fields, and the entire |    |

|      | durable queue on the <b>Intel</b> platform                             | 47 |

| 4.1  | Operation in a traversal data structure                                | 54 |

| 4.2  | Diagram for Case 1 of Lemma 4.4.1                                      | 63 |

| 4.3  | Operation in an NVTraverse data structure                              | 64 |

| 4.4  | HLL Persistent Insert                                                  | 74 |

| 4.5  | HLL Persistent Delete                                                  | 75 |

|      |                                                                        |    |

| 4.6        | HLL Persistent Find                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7        | HLL Persistent Search                                                                                                                                  |

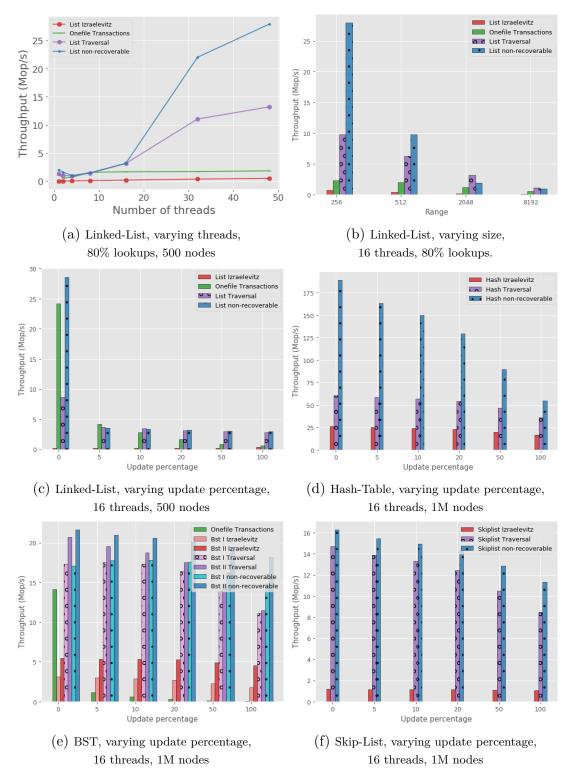

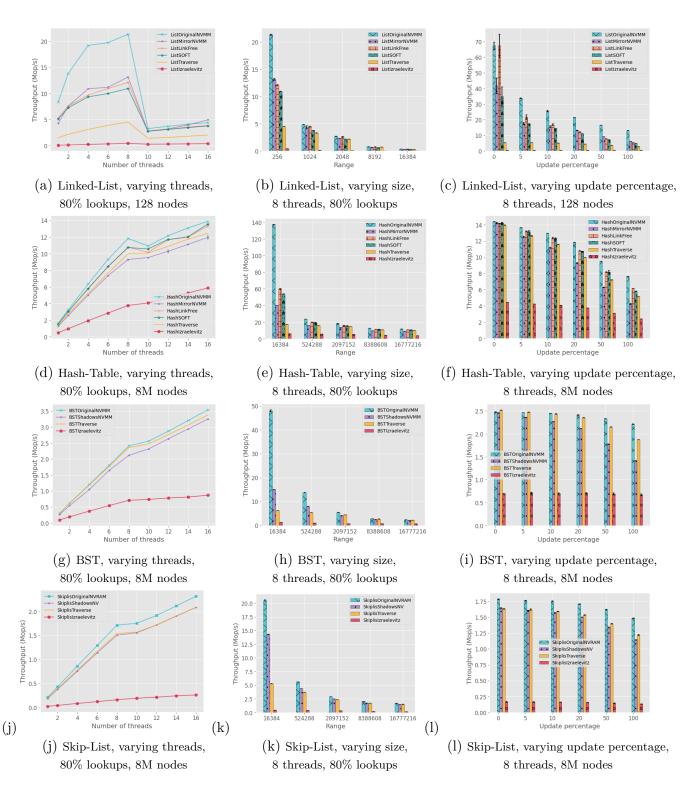

| 4.8        | NVRAM throughput results                                                                                                                               |

| 4.9        | DRAM throughput results                                                                                                                                |

| 5.1        | Example of using Mirror's Library                                                                                                                      |

| 5.2        | Patomic class                                                                                                                                          |

| 5.3        | A scenario that could cause problems if there was no sequence number $$ . $$ 89                                                                        |

| 5.4        | Patomic Compare_exchange_strong Implementation                                                                                                         |

| 5.5        | Patomic Load Implementation                                                                                                                            |

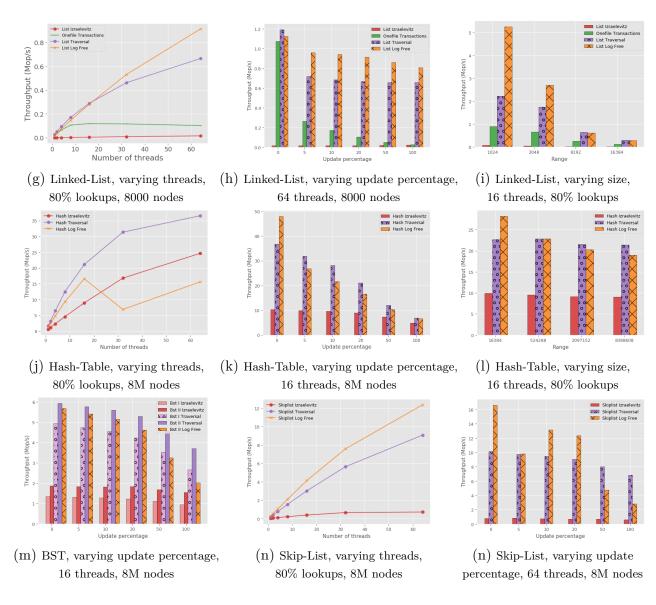

| 5.6        | NVMM throughput results with one replica of Mirror placed on DRAM. 100                                                                                 |

| 5.7        | NVMM throughput results. Both copies of Mirrors on NVMM 104                                                                                            |

| 6.1        | Basic interface of FliT                                                                                                                                |

| 6.2        | FliT library used for a concurrent BST                                                                                                                 |

| 6.3        | The Flush-Marking Algorithm                                                                                                                            |

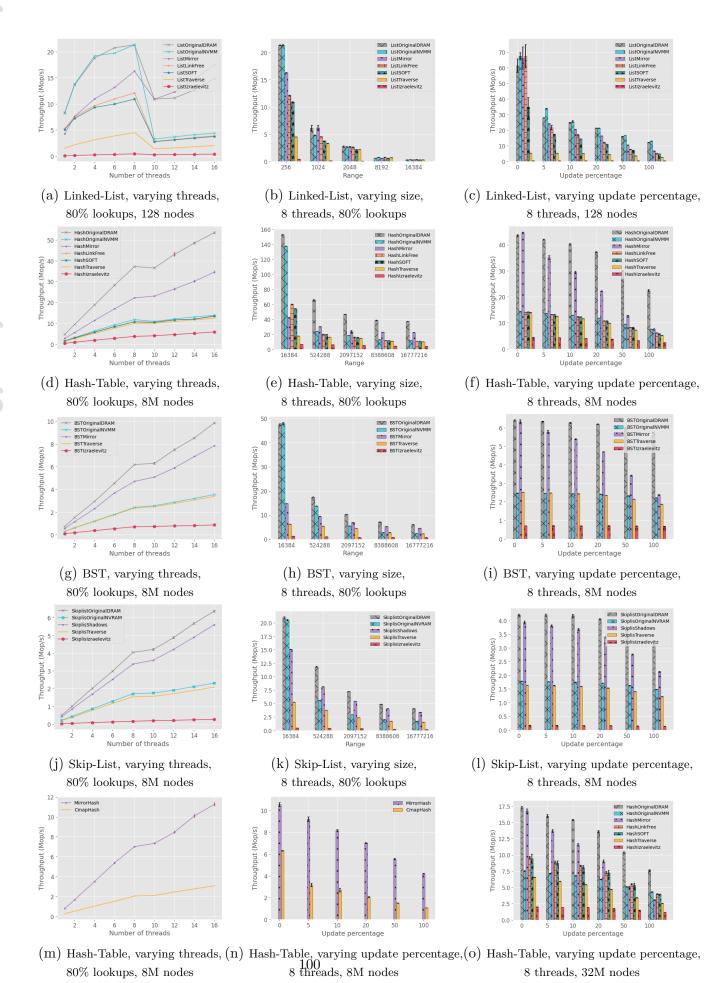

| 6.4        | Tuning Hash-Table size for the FliT library. Throughput shown is for the automatic BST with 10K keys                                                   |

| e r        | v                                                                                                                                                      |

| 6.5        | Scalability graphs for the automatic BST with 10K keys and 5% updates.123                                                                              |

| 6.6        | Throughput of 44 threads with 5% updates                                                                                                               |

| 6.7        | Throughput results for 44 threads, automatic, normalized to the through-                                                                               |

| <i>a</i> o | put of the non-persistent version of each data structure                                                                                               |

| 6.8        | Number of flushes per operation, 5% updates                                                                                                            |

| 7.1        | Recoverable CAS algorithm                                                                                                                              |

| 7.2        | Check Recoverable CAS                                                                                                                                  |

| 7.3        | CAS-Read Capsule                                                                                                                                       |

| 7.4        | Persistent Normalized Simulator                                                                                                                        |

| 7.5        | Implementing $M$ writable CAS objects using regular CAS objects. Code                                                                                  |

|            | for process $p_i \ldots \ldots$ |

| 7.6        | Recycle operation of a writable CAS object                                                                                                             |

| 7.7        | Throughput of persistent and concurrent queues under various thead                                                                                     |

|            | counts                                                                                                                                                 |

## Abstract

Memory and storage are considered major performance bottleneck of almost all computer systems. The role of computer storage, particularly secondary memory such as SSDs or HDDs, has become even more critical with the advance in technology and system design. Fortunately, the emergence of non-volatile main memory (NVMM), which provides persistence, byte-addressability, near-DRAM performance and large capacity, revolutionizes the way we use secondary memory. By using NVMM, data can be read/written directly from memory, without the need of marshaling it into a block-based format, and is crash-resilient at a minimal performance cost. Several challenges still remain, however, since caches and registers remain volatile. Consequently, the most updated application's data may be located in the cache, and is lost upon a crash. Accordingly, data structures must be designed in a way that a recovery procedure will be able to retrieve a consistent memory state following a crash. Concurrent data structures increase the difficulty of the design, as achieving correctness, efficiency, and scalability simultaneously becomes more challenging, and the involvement of experts in concurrency and durability is required.

This dissertation aims at designing efficient, durable and concurrent data structures and algorithms for NVMM. It first presents novel implementations of a concurrent lock-free queue. These implementations illustrate algorithmic challenges in building persistent lock-free data structures with different levels of durability guarantees. Additionally, we present a new notion of detectable execution. A data structure provides detectable execution if it is possible to tell at the end of a recovery phase whether a specific operation was executed. Interestingly, there was no such requirement prior to this work. Next, we introduce two general techniques for building lock-free data structures, NVTraverse and Mirror. Presented as NVM libraries, they reduce the programming effort required to add persistence to volatile data structures. Our evaluation shows that these constructions outperform other techniques for designing durable data structures by a large margin. NVTraverse is a general transformation that takes a lock-free data structure from a general class called a traversal data structure and automatically transforms it into an implementation of the data structure for the NVMM setting that is provably correct and highly efficient. Mirror is a simple, general automatic transformation that adds durability to any lock-free data structure, with a low performance overhead. Moreover, Mirror exploits the hybrid system to substantially

improve performance. The next contribution in this dissertation is FliT, a C++ library that facilitates writing efficient persistent code. Using the library's default mode makes any linearizable data structure durable with minimal changes to the code. FliT avoids many redundant flush instructions by using a novel algorithm to track dirty cache lines. Finally, our last contribution is the development of a general construction that takes any concurrent program and makes it persistent. The converted algorithm has a constant computational delay (preserves instruction counts on each process within a constant factor), as well as a constant recovery delay (a process can recover from a fault in a constant number of instructions).

### Chapter 1

## Introduction

A critical bottleneck in a program's performance is accessing the slow long-term storage unit, such as HDDs or SSDs. Intel's recent introduction of the Optane memory platform, has made a large byte-addressable memory that does not lose its content upon a crash (i.e., non-volatile) and has access speeds comparable to DRAM available. The memory can serve as a very large main memory, opening up a whole new world of opportunities in designing modern programs and systems.

Numerous recent studies have proposed various schemes to exploit the benefits of non-volatile main memory. A substantial fraction of these research projects attempts to design persistent data structures, allowing them to be manipulated by the program with no need to save their content to a secondary persistent storage, in an augmented format. Data structures form the basic blocks for any software design and facilitates better storage systems, databases, key-value stores, etc. Since traditional storage media have been block-based, all these applications persist these data structures by marshaling them into a block-based format. As a result, the in-memory representation and on-disk (SSD) representation of these data structures are quite different. Byte-addressable persistent memory can be used to create a unified persistent representation. Designing data structures and algorithms for non-volatile main memory is hard because caches and registers are still volatile, and their content, which reflects the most updated data, is lost upon a crash. Thus, there might be inconsistencies in the state of the main memory, following a crash, since it might be missing recent data writes not yet flushed from the cache into the main memory. There are, however, special instructions that flush data to the memory, in order to ensure that important data is available in the (persistent) memory after a crash. These instructions allow the programmer to make sure that certain data is written to memory, securing the state of the execution. Such flushing of data from cache to memory, nevertheless, is costly, and good algorithms use these instructions sparingly. The difficulty of the design increases in the presence of concurrent data structures as correctness, efficiency, and scalability become harder to achieve simultaneously, requiring the involvement of experts on concurrency and durability.